combinational circuits

Summary

Gate-level design

- circuit constructed with pure logic gates

- focus on the logical expression

Block-level design

- components abstracted as “black boxes”

- focus on the higher level idea of each component

Binary coded decimal(BCD)

Circuit delay

- a gate/block needs to wait for the slowest input

Concept

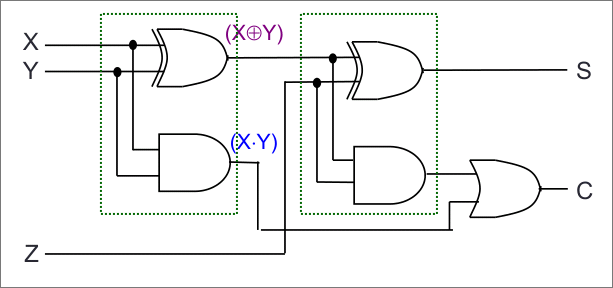

Full adder

- arithmetic addition of 3 single bits, 3rd is for the carry bit

- 2-bit output

- can be implemented using 2 half adders

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

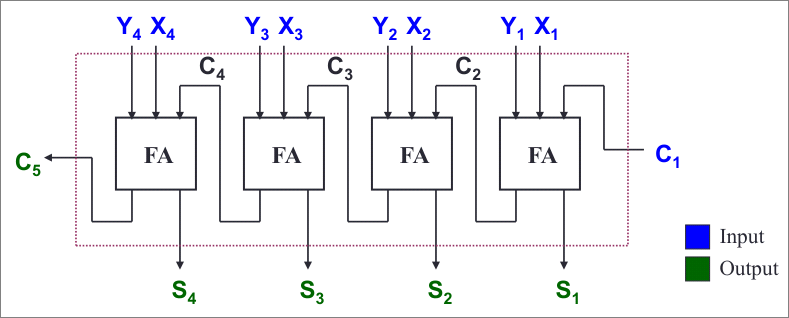

4-bit parallel adder

- arithmetic addition of two 4-bit binary numbers and a carry in

- 5-bit output

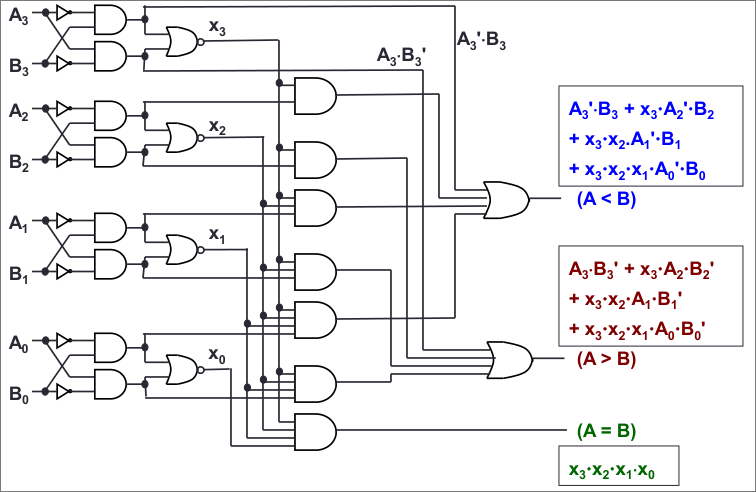

4-bit magnitude comparator

- compare two 4-bit binary numbers

- 3 outputs for

<,>and=

Application

BCD to excess-3

Extra

Expansion of XOR

Negation of XOR